삼성전자는 그동안 3D 낸드플래시 메모리 기술 개발 경쟁에서 1위를 달려왔다. 그런 삼성의 지위가 흔들리고 있다는 관측이 제기됐다.

일본 도시바메모리와 미국 웨스턴디지털(WD) 연합이 올해 3D 낸드플래시 기술 개발을 선도하기 시작했다는 조짐이 보인다고 18일(현지시간) 일본 IT 전문매체 임프레스워치가 분석했다.

임프레스워치는 반도체 기술 개발 성과를 보여주는 국제학회인 ‘국제고체회로학회(ISSCC)’의 최신 발표를 바탕으로 이런 결론을 도출했다.

삼성은 2014년 ISSCC를 기점으로 매년 눈부신 3D 낸드플래시 성과를 제시했다. 5년 전에는 저장용량 128기가비트(Gbit)에 24단 적층 구조를 채택한 낸드플래시를 소개했다. 이 메모리는 1개의 반도체 셀(소자)에 저장하는 정보가 2비트인 MLC다. 이는 세계 최초의 공식적인 3D 낸드플래시였다고 임프레스워치는 전했다.

이듬해 삼성은 용량은 128Gbit로 이전과 같지만 32단에 3비트 셀 방식인 TLC를 도입해 실리콘 면적을 대폭 줄인 3D 낸드플래시를 발표했다. 이 칩은 본격적인 3D 낸드플래시 메모리로 자리매김했다.

2016년에는 저장용량을 256Gbit로 두 배 확대했으며 메모리 밀도도 48층으로 더욱 늘린 칩을 발표했다. 이 시점에서 플래시 메모리 분야 2위인 도시바-WD 연합은 3D 낸드 칩을 ISSCC에서 아직 발표하지 못한 상태였다. 사실상 삼성의 독무대였던 것이다.

2017년 도시바-WD 연합은 512Gbit의 3D 낸드플래시 기술을 발표했다. 적층 수는 64단이었으며 TCL 방식이 적용됐다. 신기하게도 삼성도 거의 같은 사양의 제품을 선보였다. 즉 이때부터 양측의 경쟁이 시작됐다고 볼 수 있다.

지난해 양 진영의 발표는 엇갈렸다. 삼성은 64단을 유지했지만 셀에 저장하는 정보를 1비트 더 높인 4비트의 QLC를 적용한 사상 최대 용량의 3D 낸드 칩을 발표했다. 도시바-WD 연합은 적층 수를 96단으로 전년보다 1.5배 늘린 사상 최대 밀도의 칩을 선보였다. 삼성은 ‘역대 최대 용량’으로, 도시바-WD 연합은 ‘사상 최대 밀도’로 각각 최고 수준의 기술을 과시한 셈이다.

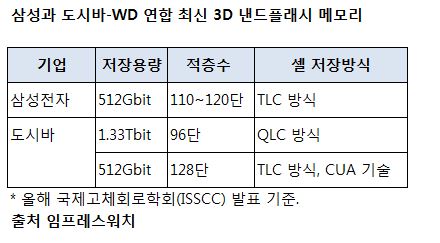

그러나 올해 ISSCC는 양상이 조금 달랐다고 임프레스워치는 지적했다. 도시바-WD 연합이 큰 폭으로 진화한 2종류의 3D 낸드 칩을 선보였지만 삼성은 과거에 비해 기술적인 진화가 그만큼 크다고 말하기 힘든 칩을 발표했다는 것이다.

구체적으로 살펴보면 도시바-WD 연합은 적층 수를 전년과 동일하게 96단으로 하면서 QLC 방식으로 변경한 칩을 발표했다. 단일 칩 저장용량은 1.33테라비트(Tbit)로 역대 최대 수준이다.

또 연합은 적층 수를 128단으로 사상 최대로 늘리고 주변 회로를 메모리 셀 어레이 바로 아래에 적층해 실리콘 면적을 절약한 3D 낸드 칩을 발표했다. 이 칩은 TLC 방식으로는 역대 최고 저장밀도를 달성했다.

반면 삼성은 적층 수를 110~120단으로 늘린 3D 낸드 칩을 발표했다. 저장용량과 저장밀도 모두 전년과 비슷한 수준으로 도시바-WD 연합에 비해 약해보였다고 임프레스워치는 평가했다.

임프레스워치에 따르면 삼성의 낸드 플래시 메모리 개발에 대한 태도 변화는 이미 지난해 8월 개최된 플래시메모리서밋(FMS)에서 처음 드러났다. 2017년까지만 해도 삼성은 FMS에서 기조연설을 하고 최대 부스를 꾸미는 것이 관례였다. 그러나 지난해는 기조연설과 부스 모두 없어 업계 관계자들을 놀라게 했다.

이는 올해 ISSCC에서 삼성의 소극적인 발표와 일맥상통하는 것이라고 임프레스워치는 지적했다.

![다시 아이바오의 시간…푸루후 동생 향한 마음들 [해시태그]](https://img.etoday.co.kr/crop/140/88/2337223.jpg)

![‘뛰지 마’만 남은 학교…피해는 결국 학생들 [사라지는 교실 밖 교실 下-①]](https://img.etoday.co.kr/crop/140/88/2336652.jpg)

![스페이스X 800억달러 IPO, 한국 공모 시장과 비교하면? [인포그래픽]](https://img.etoday.co.kr/crop/140/88/2337128.jpg)

![주문 늘어날수록 적자? 벼랑 끝에 내몰린 100만 자영업자의 눈물 [T같은F]](https://i.ytimg.com/vi/SS61xAnb_n4/mqdefault.jpg)

![“술 한 잔도 부담”...소주 7000원 시대, 자영업자·소비자 모두 무너진다 [T 같은 F]](https://img.etoday.co.kr/crop/300/170/2337256.jpg)

![영장심사 출석하는 김대기 전 비서실장 [포토]](https://img.etoday.co.kr/crop/300/190/2337228.jpg)